## Institute for Complex Systems (ICS)

Univ.-Prof. Dr.-Ing. Daniel Große

Web: jku.at/ics

Email: daniel.grosse@jku.at

### news **ORF.at**

CHIPGIGANT ARM

### Poker um Deal mit weltweiten Folgen

Ein geplanter Megadeal in der Chipbranche sorgt für Kritik von Wettbewerbshütern auf der ganzen Welt: Das US-Unternehmen Nvidia will den britischen Chipdesigner Arm kaufen, dessen Technologie den Kern jedes modernen Smartphones bildet. Bisher gehörte Arm dem japanischen Telekomkonzern SoftBank und galt damit praktisch als "neutral" - dass Arm nun in US-Hand kommen soll, beunruhigt nicht nur China.

8. September 2021, 18.52 Uhr

#### Worst-Case-Szenario als Chance für offene Alternative

Sollte die Übernahme von Arm durch Nvidia tatsächlich Auswirkungen auf die weltweite Rechnerproduktion haben, könnte das - zumindest längerfristig - dazu führen, dass sich Hersteller nach Alternativen zu den Arm-Designs umsehen. Einen Kandidaten - bisher grober Außenseiter - gibt es dafür schon. Mit RISC-V existiert ein Konkurrenzstandard mit einem enormen Vorteil: Die Rechnerarchitektur ist offen verfügbar - das heißt, für die Verwendung in Chips fällt an sich keine Lizenzgebühr an.

### tom's HARDWARE

Reviews

**Best Picks**

Intel Offers \$2 Billion for RISC-V Chip Startup SiFive: Bloomberg

By Paul Alcorn June 10, 2021

## System-on-Chip (SoC)

- Omnipresent + very complex

- Heart: Processor

- Very hot: RISC-V

### RISC-V-Prozessoren fliegen in Weltraum

I 12.09.2022 18:08 Uhr Christof Windeck

Die NASA setzt beim High-Performance Spaceflight Computing (HPSC) künftig auf RISC-V. Ein europäischer Nanosat mit RISC-V-CPU umkreist bereits die Erde.

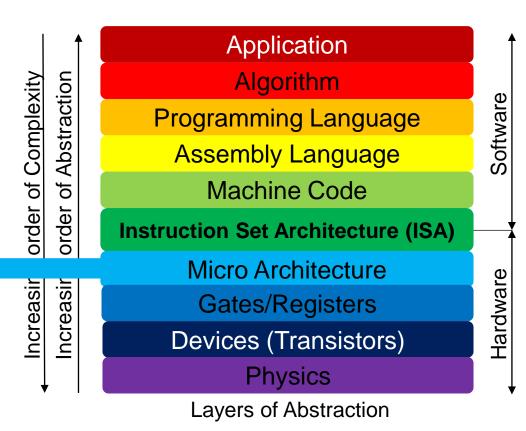

## **Instruction Set Architecture (ISA)**

- Instruction Set Architecture (ISA) is the interface between HW and SW

- Instructions (encoding & semantics)

- Number and types of registers

- Memory access, addressing modes

## **Modular Design**

Intel x86, ARM

Incremental instruction set

**RISC-V**Composable extensions

# Disruptive **Technology**

### **Barriers**

Complexity

Design freedom

License and Royalty fees

Design ecosystem

Software ecosystem

Specification

## **Legacy ISA**

1500+ base instructions Incremental ISA

\$\$\$ – Limited

\$\$\$

Moderate

Extensive

180 hours to read

### **RISC-VISA**

47 base instructions Modular ISA

Free – Unlimited

Free

Growing rapidly. Numerous extensions and cores. More design companies on RISC-V than any other architecture

Growing rapidly. Easy to compile for RISC-V

6 hours to read

RISC-V is an open standard

## **Bachelor Thesis**

I want to implement my own processor!

I want to work on SW side or programming languages!

### Contact us

- Together we will work out the topic of your thesis

- Depending on your interests

- Already have an idea? Great!

- We support you at every stage of your thesis

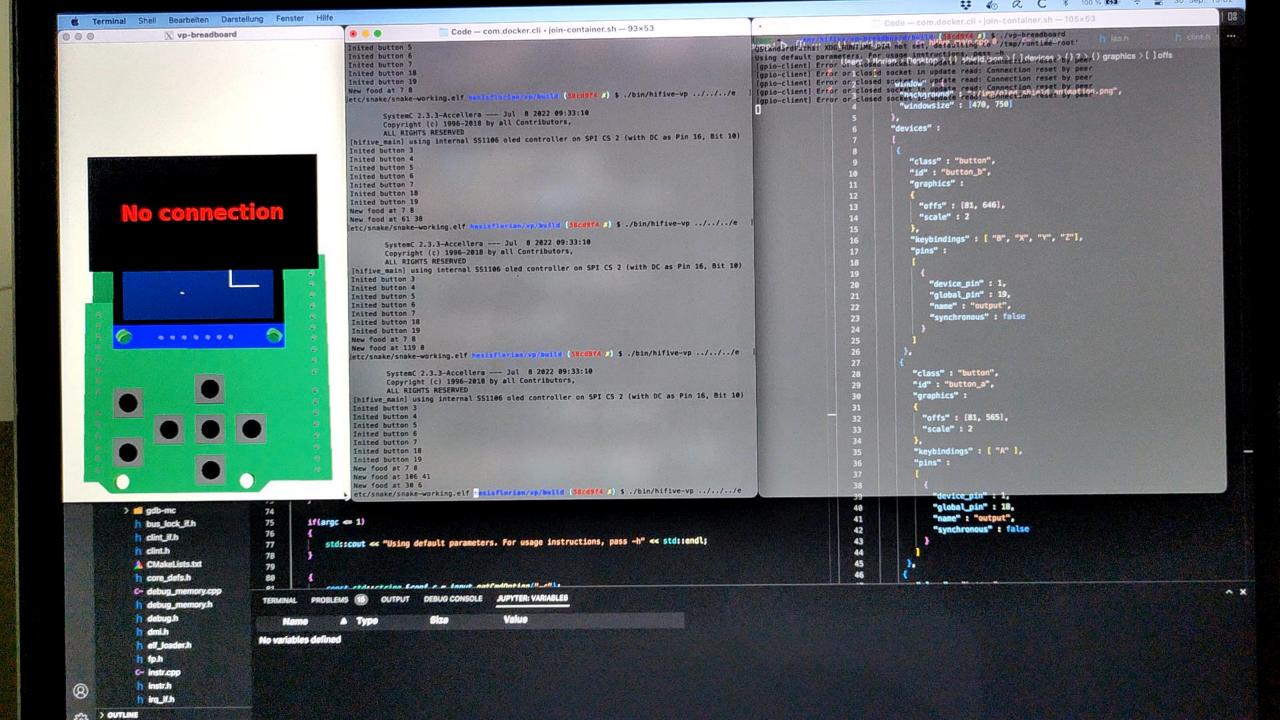

A very cool result

And a new title for your collection

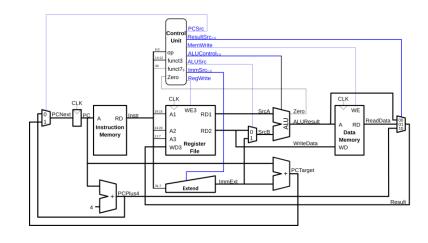

## **Research Areas at our Institute**

- Modelling & Implementation

- RISC-V virtual prototypes

- RISC-V cores (VHDL, Verilog)

- SUBLEQ Processor (processor in 1 instruction)

- Accelerators (RISC-V Vector extension, NNs, Approximate Computing)

- ° ...

- Electronic Design Automation: e.g. verification

- Fuzzing

- Domain Specific Programming Languages

- Metamorphic Testing

- Symbolic execution of SW interacting w HW

- Symbolic Computer Algebra (SCA) for hard arithmetic (e.g. multipliers) at gate level

# Institute for Complex Systems (ICS)

Univ.-Prof. Dr.-Ing. Daniel Große

Web: jku.at/ics

Email: daniel.grosse@jku.at

See also: https://ics.jku.at/teaching/theses/